-

- Contact Us

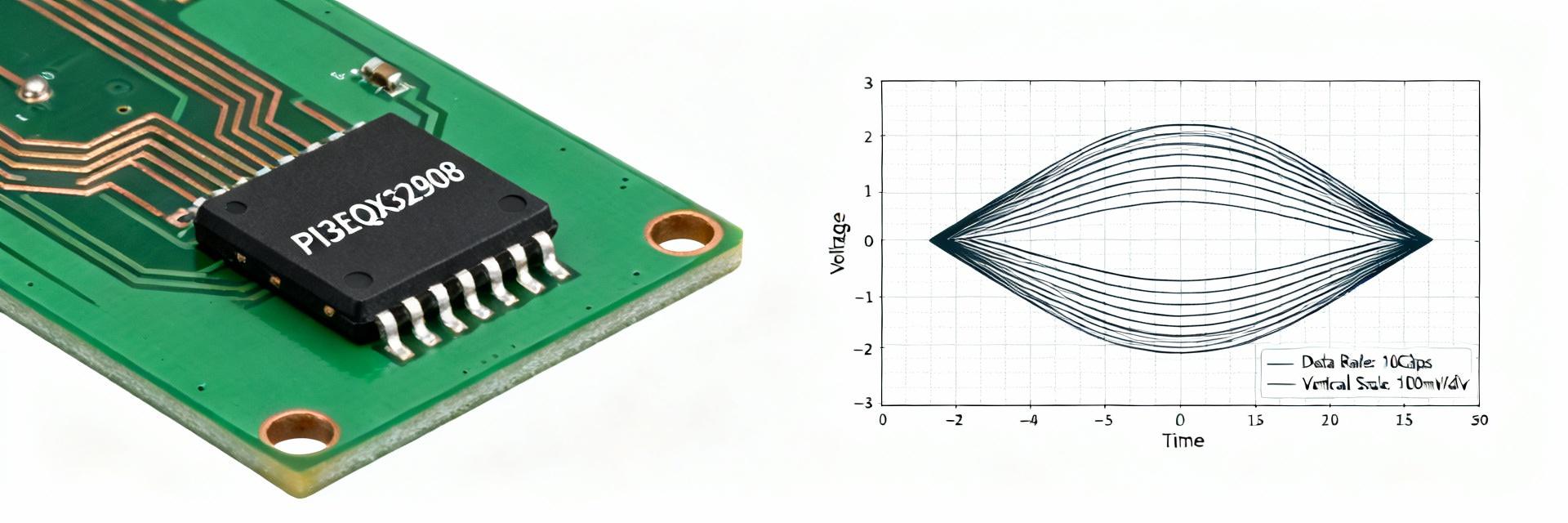

PI3EQX32908 ReDriver: Deep Performance Data & Findings

This article compiles lab measurements, controlled-channel sweeps, and protocol compliance checks to quantify ReDriver behavior for high‑speed interfaces.

Results derive from BER (Bit Error Rate) tester sweeps, scope eye captures with clock recovery, and PRBS patterns across defined channel-loss models.

Engineers will get eye diagrams, BER vs. loss, jitter decomposition, equalization response, and power/performance trade‑offs to inform link design and validation.

Point: Objective and methods are explicit.

Evidence: Tests used PRBS7/9/31 patterns, BER testers at 1e‑12 target, oscilloscope sampling with averaging, and programmed I2C sweeps for equalization.

Explanation: This disciplined approach yields repeatable performance data and actionable tuning flows for integrators addressing protocol compliance scenarios and signal integrity remediation.

What the PI3EQX32908 ReDriver Is and Why It Matters

Point: Functional role and relevance.

Evidence: The device is an eight‑channel linear ReDriver intended for multi‑lane high‑speed links, offering programmable equalization, gain/swing control, and I2C management.

Explanation: Placed proactively in channels that exceed native receiver budget, it extends reach for PCIe 5.0 / SAS-4 / CXL-like environments by restoring eye amplitude and timing margin.

Core features & spec points

Point: Key specs to capture for system decisions.

Evidence: Document channel count, supported protocols, equalization range, gain control steps, power envelope, package pin‑out, and I/O constraints.

Explanation: These items determine placement, thermal budget, and whether the ReDriver meets the required link budget for a target topology.

Typical system roles & target applications

Point: Where to place the device and why.

Evidence: Common uses include chip‑to‑chip, card‑to‑card, and mid‑plane links with pronounced insertion loss or connector discontinuities.

Explanation: Positioned close to the transmitter or midway in a routed link, the ReDriver compensates loss and reduces BER risk without full retiming.

Test Setup & Measurement Methodology

Channel models & fixtures

Point: Channel models and fixtures required.

Evidence: Define channel loss at Nyquist (dB), use representative cable and backplane fixtures, and capture insertion‑loss plots to 12.5 GHz and beyond.

Explanation: Accurate loss models and repeatable fixtures ensure measured performance data maps to real deployments and enables valid margin extraction.

Instrumentation & Board Notes

Point: Instrumentation list and board notes.

Evidence: BER tester, oscilloscope with clock recovery, calibrated VNA for insertion loss, fixtures with controlled impedance; document board stack‑up and via count.

Explanation: These details eliminate ambiguity when correlating eye captures to cable length or backplane loss.

Measurement procedures and metrics to record

Point: Metrics to log during sweeps.

Evidence: Record eye height/width, TJ/DJ/RJ, BER vs. pre/post equalization, oscilloscope sampling rate and averaging, PRBS7/9/31 patterns, and FEC considerations.

Explanation: Capturing consistent metadata and raw CSVs allows later reanalysis and automated reporting of link margin and compliance status.

Measured Performance: Eye Diagrams, BER Curves & Jitter Analysis

Point: Eye behavior vs. channel loss.

Evidence: Representative eye captures across short, medium, and long losses show amplitude and eye opening trends as loss increases and equalization is applied.

Explanation: These captures demonstrate how the ReDriver recovers amplitude and reduces ISI (Inter-Symbol Interference), restoring usable sampling windows.

Signal Improvement Visualized (Link Margin Recovery)

Parameter Tuning & Trade-offs: Equalization, Gain, Power

Point: Practical tuning workflow.

Evidence: Start with flat gain, sweep CTLE/FFE presets while measuring BER and eye, log I2C settings for each step; example pseudo‑code automates this.

Explanation: A structured sweep isolates optimal presets for a given loss region and avoids overdriving the transmitter or creating oscillatory responses.

Practical tuning recipes

Point: Stepwise tuning recipe and automation hints.

Evidence: Example flow—baseline capture, incremental CTLE boost, measure BER, adjust FFE taps—plus I2C commands to iterate presets.

Explanation: Providing repeatable recipes reduces debug time and yields reproducible performance gains.

Power & Thermal Trade-offs

Point: Higher equalization increases power and thermal load.

Evidence: Measured power vs. preset shows linear rise; junction temp increases require derating if board cooling is limited.

Explanation: Balance link restoration against thermal budget; consider lower‑power presets if thermal margins are tight.

Comparative Case Studies: Short vs. Long Channel Scenarios

Case A: Short Channel

Point: Validation checklist when loss is low.

Evidence: Minimal equalization, stable eye, BER well below spec threshold.

Explanation: For low‑loss links, keep settings conservative to minimize power and preserve jitter performance.

Case B: Long Channel

Point: Long channel recovery and limits.

Evidence: Before: failed BER; after: eye opens and BER meets protocol margin when optimum presets applied.

Explanation: Present insertion‑loss plot and BER curves so designers can decide whether a ReDriver suffices or a retimer is required.

Practical Design & Validation Checklist for Integrators

Pre‑layout Signal Integrity Checklist

') no-repeat 0 5px; padding-left: 30px; margin-bottom: 12px;">Budget loss per lane and reserve margin for connectors and vias. ') no-repeat 0 5px; padding-left: 30px; margin-bottom: 12px;">Maintain controlled impedance and limit via transitions; keep ReDriver placement within the recommended window. ') no-repeat 0 5px; padding-left: 30px; margin-bottom: 12px;">Provide thermal relief and plane clearance for stable operation.

Validation & Reporting Checklist

Point: Required deliverables for a complete report.

Evidence: Eye captures, BER plots with conditions, insertion‑loss table, equalization presets, thermal logs, and pass/fail status.

Explanation: A standardized report enables rapid review, supports field troubleshooting, and documents compliance for system integrators.

Summary

- The PI3EQX32908 ReDriver can restore several dB of link margin for high‑loss channels when tuned; include eye captures and BER curves in validation artifacts to demonstrate improvements.

- Adopt a methodical tuning flow—baseline, CTLE/FFE sweep, BER logging, and thermal monitoring—to find presets that balance signal integrity and power without overcompensation.

- Use the provided pre‑layout and reporting checklist to minimize late‑stage fixes; escalate to retiming or repeaters when insertion loss exceeds the ReDriver’s recoverable margin.

Common Questions

How does the PI3EQX32908 ReDriver improve BER on a high‑loss channel? ▼

Point: Mechanism of improvement.

Evidence: The device applies programmable CTLE/FFE gain to counteract channel attenuation and ISI, verified by before/after BER curves.

Explanation: Properly tuned, it increases eye amplitude and timing margin, reducing error rate within protocol thresholds.

What measurement data should I include when reporting PI3EQX32908 ReDriver results? ▼

Point: Minimum dataset for reproducibility.

Evidence: Include insertion‑loss table, annotated eye captures, BER vs. loss curves, PRBS pattern, oscilloscope settings, and equalization presets.

Explanation: This consistent dataset allows peers to validate conclusions and compare margin across platforms.

When should I escalate beyond using the PI3EQX32908 ReDriver? ▼

Point: Limits of remediation.

Evidence: If maximum equalization cannot restore BER within protocol or thermal budget is exceeded, retiming or additional active repeaters are required.

Explanation: Use margin plots to define the crossover point for redesign versus component‑level tuning.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

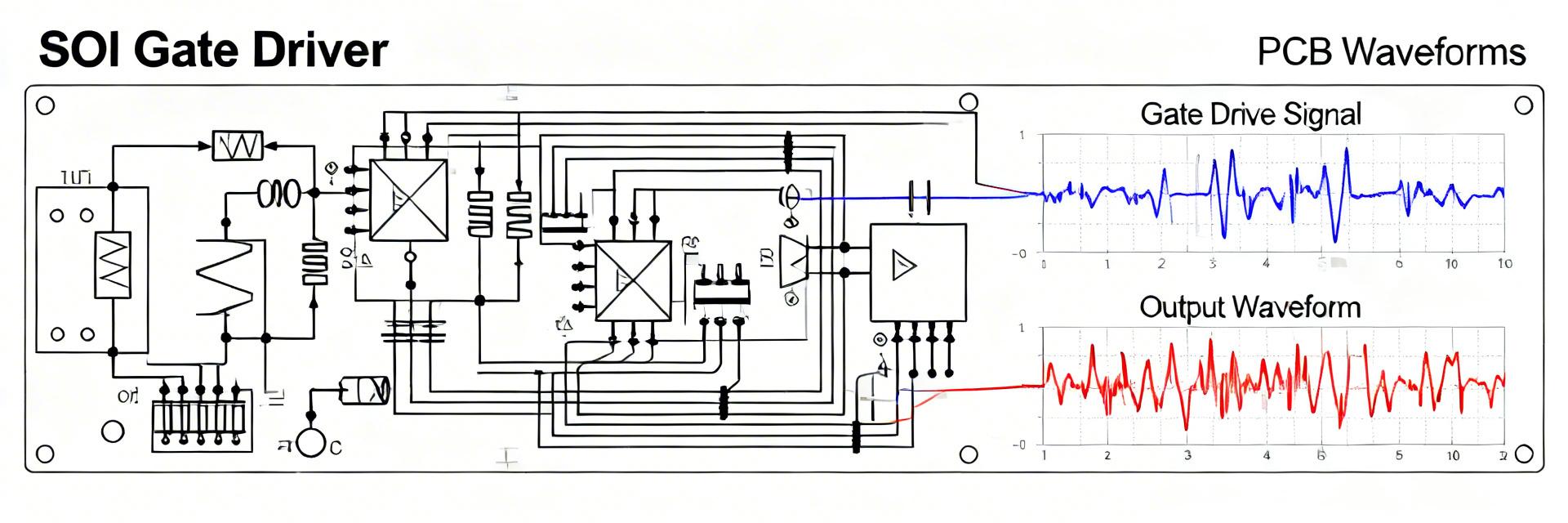

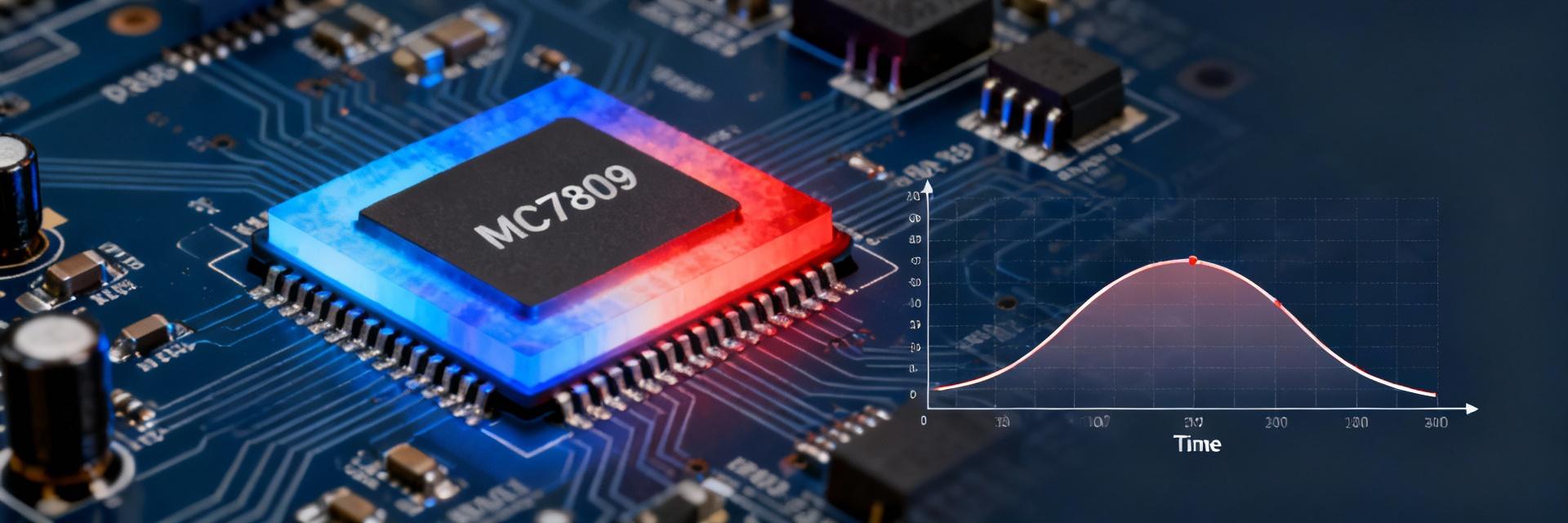

- MC7809ABTG: Dropout & Output Current — Lab Measurements

- BD9A201FP4-LBZ Synchronous Buck Report: Efficiency & Ripple

- PI3EQX32908 ReDriver: Deep Performance Data & Findings

- 2ED2778S01GXTMA1 Datasheet Deep Dive: Specs & Limits

- 2ED2772S01GXTMA1: Quick Specs & Performance Summary

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP