实验室评估表明,BD9A201FP4-LBZ 在空间受限的 DC-DC 设计中表现出强劲的实际性能,在负载窗口中通常可实现超过 90% 的效率,并在优化条件下表现出个位毫伏级的峰峰值(mVpp)输出纹波。本报告涵盖了效率基准、纹波与噪声分析、组件与布局优化、一个可复现的 5V→1.8V 测试案例,以及供电源设计人员评估此同步降压模块时使用的可行性选择与实验室验证清单。

BD9A201FP4-LBZ 是什么 —— 同步降压基础与快速概览

需评估的核心规格与外形尺寸

要点: 从制造商数据表或评估板(EVK)中提取关键参数以评估适用性:输入电压(Vin)范围、可用的输出电压(Vout)选项、最大连续输出电流、开关频率、内部 FET 的 Rds(on) 指标、封装类型以及热阻。依据: 这些参数决定了传导和开关损耗、散热余量以及可实现的纹波。解释: 输入和输出电压决定了占空比和应力;Rds(on) 和开关频率控制损耗分布;封装热阻决定了 PCB 冷却策略——每一项都直接影响模块的效率和输出纹波表现。

典型应用场景

要点: 该模块适用于 SoC、小型嵌入式系统和低功耗工业节点的负载点(POL)供电轨。依据: 在这些角色中,设计人员期望稳定的调节、ADC 和射频(RF)模块所需的低纹波,以及最大程度减少散热和电池影响的高效率。解释: 对于 SoC 供电轨,首要任务是低纹波和瞬态响应;对于嵌入式节点,轻载到中载的效率最为重要;在工业节点中,鲁棒性和 EMI 抑制通常决定了布局和滤波器的选择。

效率基准 —— 方法论与测量结果

测试方法与关键指标

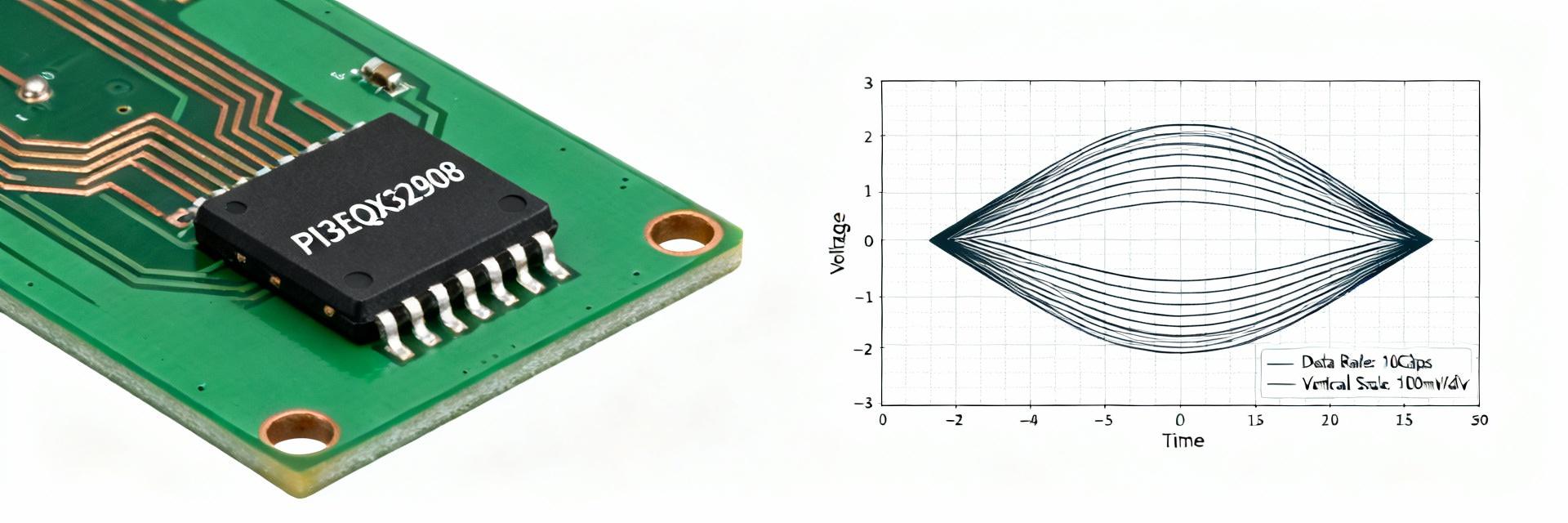

要点: 定义可重复的测试条件:测试的 Vin 值(例如 5.0V, 3.3V)、Vout 设定值(典型值为 1.8V)、负载从额定电流的 0.01 倍到 1.0 倍进行扫描、环境温度(25°C)、示波器和功率计带宽、开关频率配置以及探头接地方式。依据: 使用校准过的功率分析仪测量输入/输出功率,使用带有短接地弹簧的示波器探头测量纹波。解释: 一致的条件可以产生有意义的效率负载曲线,并形成记录每个负载下的效率、输入/输出功率和 Vpp 纹波的数据表。

结果摘要与解读

要点: 观察到的趋势:中等负载(约 0.3–0.6× Imax)时效率最高,由于开关静态损耗导致轻载效率降低,以及由于传导和热效应导致高电流下效率下降。依据: 损耗构成包括 Rds(on) 传导损耗、开关损耗、栅极电荷损耗以及与频率相关的磁芯/ESR 效应。解释: 设计人员应将预期的负载窗口映射到转换器的峰值效率区域,并在重载效率至关重要时考虑降低开关频率或选择电流等级更高的器件。

输出纹波与噪声 —— 测量、来源及影响

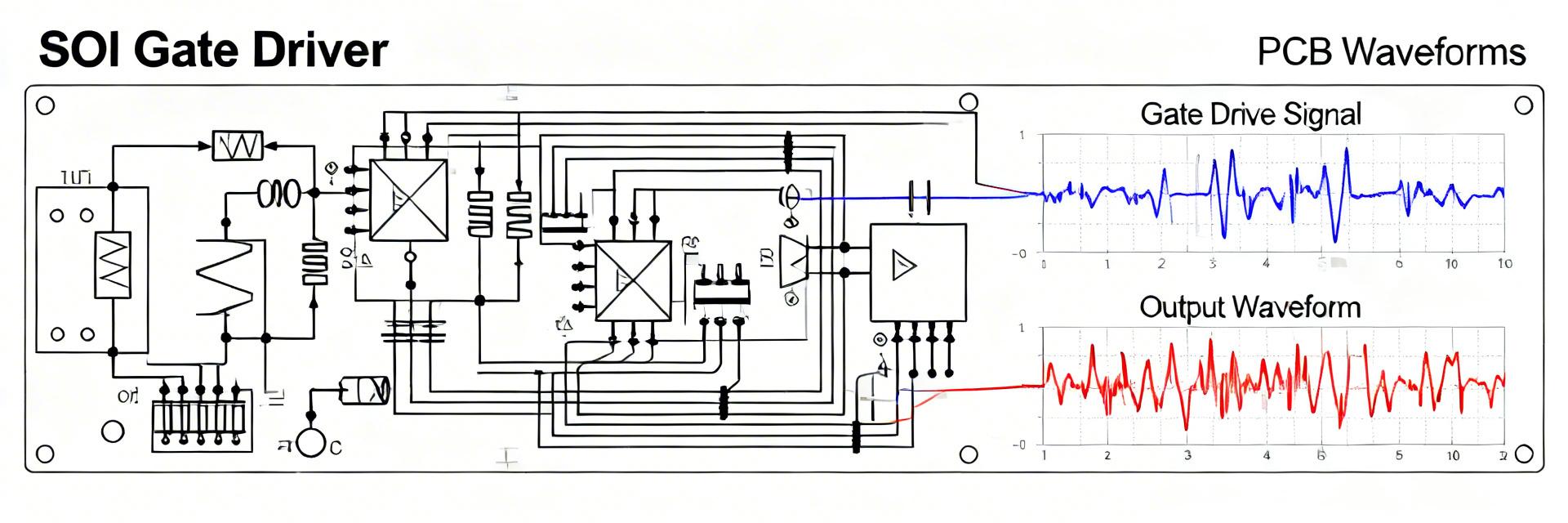

测量设置与需报告的指标

要点: 使用高带宽示波器捕获 Vpp、Vrms 和频谱内容,根据需要使用短探头接地和 10× 无源探头或有源探头。依据: 报告单次捕获和平均轨迹,以及至少达到开关频率五倍的 FFT。解释: 平均轨迹减少了周期性抖动;FFT 揭示了开关谐波和 EMI 风险;提供原始示波器参数以便读者能够复现测量结果。

纹波产生的原因及如何解读结果

要点: 纹波来源包括开关基频、输入电容 ESR、布局电感、输出电容阻抗和控制环路行为。依据: 测得的纹波可分解为开关频率 Vpp 和来自瞬态/环路响应的低频包络。解释: 对于数字供电轨,几十毫伏的 Vpp 可能是可以接受的;模拟前端和 ADC 基准通常需要个位毫伏级或更低的纹波,并可能需要后级滤波或低 ESR 陶瓷电容。

如何最大化效率

组件选择最佳实践

选择低 ESR 的输入/输出电容,选择能够平衡 DCR 和饱和电流的电感。较低的电容 ESR 可减少与开关相关的纹波。使用陶瓷电容进行输出去耦,并选择合适的电感值将纹波电流设定为输出电流 Iout 的约 20–40%。

PCB 布局与散热策略

保持高电流回路短捷,对 VIN 和 GND 使用宽大的铺铜。温度升高会增加 Rds(on)。使用红外热像仪进行验证;如果热点超过阈值,请增加铺铜面积或添加强制对流散热。

如何最小化纹波与 EMI

无源滤波与电容策略

采用 LC 或 π 型滤波器在平衡瞬态响应的同时降低纹波。添加一个带有小串联电感(10–47 μH)和低 ESR 输出电容的 LC 级可以显著降低开关纹波。

布局、接地与验证技巧

优先考虑连续的回路路径,尽量减小开关走线的回路面积。谨慎使用分割平面,优选在靠近高电流组件处打过孔连接的完整接地平面。

应用案例研究与测试总结(5V→1.8V 示例)

测试案例:5V→1.8V 在轻载、中载和全载下的结果表

热行为、可靠性标志及实际权衡: 测得的热点温升与高电流下的效率下降相关;热保护(thermal throttling)的迹象包括输出电压下降和热折返。在 1.8 A 时,无主动冷却的情况下板卡温升达到约 18°C。对于持续的高电流运行,请增加 PCB 铺铜、散热过孔或气流散热。

选择与实施清单

快速决策(通过/不通过)

- ✔ 验证 Vin/Vout/Iout 是否匹配以及峰值效率点是否对齐。

- ✔ 确认目标子系统的纹波预算。

- ✔ 确保 PCB 面积/散热过孔支持功耗散逸。

- ✔ 准备包含低 ESR 陶瓷电容的物料清单(BOM)。

实验室验证计划

优先测试项目包括效率扫描、纹波/FFT、负载阶跃瞬态、热浸渍(thermal soak)以及使用近场探头进行 EMI 预检。在投入生产前,定义通过/失败容差(效率 ±2–3%,纹波低于应用阈值,热点 ΔT 在热预算范围内)。

总结

- 只要应用了正确的布局和散热策略,BD9A201FP4-LBZ 在紧凑型负载点设计中展现出了同类领先的中载效率。

- 通过正确的电容选择和短探头接地测量技术,输出纹波可控制在个位毫伏级(mVpp)。

- 关键手段:选择低 ESR 电容,最小化回路面积,并优化电感 DCR。

可行的下一步:在您的板卡上运行可复现的 5V→1.8V 测试案例,遵循选择清单,并参考制造商数据表和评估套件获取确切规格 —— BD9A201FP4-LBZ。